I2C bus — pagtatalaga, aparato, paglilipat ng data, pagtugon

Kapag lumilikha ng isang electronic circuit, maraming mga developer ang nahaharap sa pangangailangan na gumamit ng isang malaking bilang ng mga intermediate chips para sa pagtutugma, pag-sample at pagtugon sa mga indibidwal na bloke nito. Upang mabawasan ang bilang ng mga auxiliary chip, iminungkahi ng Philips ang isang two-wire bidirectional I2C serial network interface noong 1980s, na partikular na idinisenyo upang pamahalaan ang maraming chips sa loob ng isang device.

Sa ngayon, ang Philips lang ang gumagawa ng higit sa isang daang I2C-compatible na device para sa electronic equipment na may malawak na iba't ibang layunin: memory, video processor system, analog-to-digital at digital-to-analog converter, display driver, atbp.

Ang I2C bus ay isang pagbabago ng serial data exchange protocol na may kakayahang magpadala ng serial 8-bit na data sa karaniwang "mabilis" na mode sa mga rate na 100 hanggang 400 kbps. Ang proseso ng pagpapalitan ng data ay ipinapatupad dito sa dalawang wire lamang (hindi binibilang ang karaniwang wire): linya ng SDA para sa data at linya ng SCL para sa pag-synchronize.

Nagiging bi-directional ang bus dahil sa katotohanan na ang mga cascade ng output ng mga device na konektado sa bus ay may mga bukas na collectors o channels, kaya ginagaya ang AND wiring. Bilang resulta, pinaliit ng bus ang bilang ng mga koneksyon sa pagitan ng mga chip, na nag-iiwan ng mas kaunting kinakailangang mga pin at bakas sa board. Bilang isang resulta, ang board mismo ay lumalabas na mas simple, mas compact at teknolohikal na mas advanced sa produksyon.

Binibigyang-daan ka ng protocol na ito na huwag paganahin ang mga address decoder at iba pang panlabas na lohika ng negosasyon. Ang bilang ng mga chips na maaaring gumana nang sabay-sabay sa I2C bus ay limitado sa kapasidad nito — maximum na 400 pF.

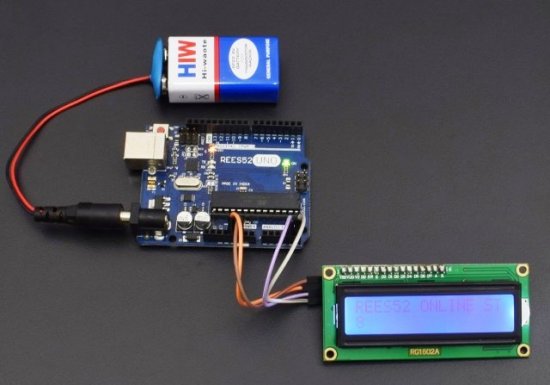

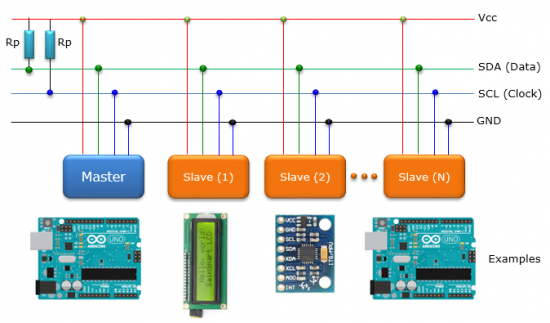

Ang mga I2C-compatible na IC ay mayroong hardware noise suppression algorithm upang matiyak ang integridad ng data kahit na may matinding interference. Ang mga naturang device ay may interface na nagbibigay-daan sa microcircuits na makipag-usap sa isa't isa kahit na magkaiba ang kanilang supply voltages. Sa figure sa ibaba, maaari mong pamilyar ang iyong sarili sa prinsipyo ng pagkonekta ng ilang microcircuits sa pamamagitan ng isang karaniwang bus.

Ang bawat isa sa mga device na nakakonekta sa bus ay may sariling natatanging address, ito ay tinutukoy nito at, alinsunod sa layunin ng device, maaari itong gumana bilang isang receiver o bilang isang transmitter. Kapag nagpapadala ng data, ang mga device na ito ay maaaring master (master) o alipin (slave). Ang master ay ang device na nagpapasimula ng paglipat ng data at bumubuo ng mga signal ng orasan sa linya ng SCL. Ang alipin, na may kaugnayan sa panginoon, ay ang patutunguhang aparato.

Sa anumang naibigay na sandali ng pagpapatakbo sa I2C bus, isang device lamang ang maaaring kumilos bilang master; bumubuo ito ng signal sa linya ng SCL.Ang isang master ay maaaring maging isang master receiver o isang master transmitter.

Sa prinsipyo, pinapayagan ng bus ang maraming iba't ibang mga masters, ngunit nagpapataw ng mga paghihigpit sa mga katangian ng pagbuo ng mga signal ng kontrol at pagsubaybay sa katayuan ng bus; Nangangahulugan ito na maraming mga master ang maaaring magsimulang magpadala sa parehong oras, ngunit ang mga salungatan ng ganitong uri ay inalis salamat sa arbitrasyon, iyon ay, ang paraan ng pag-uugali ng master kapag nakita nito na ang bus ay inookupahan ng isa pang master.

Ang pag-synchronize ng isang pares ng mga device ay tinitiyak ng katotohanan na ang lahat ng mga device ay konektado sa bus, na bumubuo ng isang "AT" na mga kable. Sa una, ang SDA at SCL signal ay mataas.

MAGSIMULA at HUMINTO

Ang palitan ay nagsisimula sa master na bumubuo ng estado ng «START»: sa linya ng SDA, ang signal ay mula sa mataas hanggang sa mababang estado, habang ang linya ng SCL ay may matatag na mataas na antas. Ang lahat ng mga aparato na konektado sa bus ay nakikita ang sitwasyong ito bilang isang utos upang simulan ang palitan.

Ang bawat master ay bumubuo ng isang indibidwal na signal ng orasan sa linya ng SCL kapag nagpapadala ng data sa bus.

Ang palitan ay nagtatapos sa pagbuo ng STOP state ng master: sa SDA line ang signal ay nagbabago mula mababa hanggang mataas, habang ang SCL line ay may matatag na mataas na antas.

Ang driver ay palaging gumaganap bilang ang pinagmulan ng START at STOP signal. Sa sandaling maayos ang signal ng «START», nangangahulugan ito na abala ang linya. Libre ang linya kapag may nakitang STOP signal.

Kaagad pagkatapos ideklara ang estado ng START, pinababa ng master ang linya ng SCL at ipinapadala ang pinaka makabuluhang bit ng unang byte ng mensahe sa linya ng SDA. Ang bilang ng mga byte sa isang mensahe ay hindi limitado.Ang mga pagbabago sa linya ng SDA ay pinagana lamang kapag ang antas ng signal sa linya ng SCL ay mababa. Wasto ang data at hindi dapat baguhin lamang kapag mataas ang pulso ng pag-sync.

Ang pagkilala na ang byte mula sa master transmitter ay natanggap ng slave receiver ay ginagawa sa pamamagitan ng pagtatakda ng isang espesyal na acknowledge bit sa linya ng SDA pagkatapos matanggap ang ikawalong data bit.

ANG CONFIRMATION

Kaya, ang pagpapadala ng 8 bits ng data mula sa transmitter patungo sa receiver ay nagtatapos sa dagdag na pulso sa linya ng SCL kapag bumaba ang receiving device sa linya ng SDA, na nagpapahiwatig na natanggap na nito ang buong byte.

Ang kumpirmasyon ay isang mahalagang bahagi ng proseso ng paglilipat ng data. Ang master ay bumubuo ng isang sync pulse. Ang transmitter ay nagpapadala ng mababang estado sa SDA habang aktibo ang acknowledge clock. Habang mataas ang pulso ng pag-sync, dapat panatilihing mababa ng receiver ang SDA.

Kung ang patutunguhang alipin ay hindi kinikilala ang address nito, halimbawa dahil ito ay kasalukuyang abala, ang linya ng data ay dapat na mataas ang posisyon. Ang master ay maaaring magbigay ng STOP signal upang i-abort ang dispatch.

Kung ang pagtanggap ay isinasagawa ng master receiver, pagkatapos ay obligado na ipaalam sa tagapaghatid ng alipin pagkatapos makumpleto ang paghahatid - hindi sa pamamagitan ng pagkumpirma ng huling byte. Ang tagapaghatid ng alipin ay naglalabas ng linya ng data upang ang master ay makapag-isyu ng STOP signal o isang paulit-ulit na START signal.

Ang pag-synchronize ng mga device ay sinisiguro ng katotohanan na ang mga koneksyon sa linya ng SCL ay ginawa ayon sa prinsipyong "AT".

Ang master ay walang tanging karapatan na kontrolin ang paglipat ng linya ng SCL mula mababa hanggang mataas.Kung ang alipin ay nangangailangan ng mas maraming oras upang iproseso ang isang natanggap na bit, maaari nitong independiyenteng panatilihing mababa ang SCL hanggang sa handa itong tumanggap ng susunod na bit ng data. Ang linya ng SCL sa ganoong sitwasyon ay magiging mababa sa tagal ng pinakamahabang low-level na pulso ng pag-sync.

Ang mga device na may pinakamababang napapanatiling mababa ay mananatiling idle hanggang sa matapos ang mahabang panahon. Kapag natapos na ng lahat ng device ang mababang panahon ng pag-sync, magiging mataas ang SCL.

Ang lahat ng mga device ay magsisimulang mag-clocking ng mataas at ang unang device na makumpleto ang panahon nito ay ang unang magtatakda ng linya ng SCL na mababa. Bilang resulta, ang tagal ng mababang estado ng SCL ay matutukoy ng pinakamahabang mababang estado ng pulso ng pag-synchronize ng isa sa mga device, at ang tagal ng mataas na estado ay matutukoy ng pinakamaikling panahon ng pag-synchronize ng isa sa mga mga device.

Ang mga signal ng pag-synchronize ay maaaring gamitin ng mga receiver bilang isang paraan ng pagkontrol ng paghahatid ng data sa antas ng bit at byte.

Kung ang device ay may kakayahang tumanggap ng mga byte sa mataas na rate, ngunit nangangailangan ng isang tiyak na tagal ng oras upang maiimbak ang natanggap na byte o maghanda upang matanggap ang susunod na byte, maaari itong patuloy na panatilihing mababa ang SCL pagkatapos matanggap at kilalanin ang isang byte, na pinipilit ang transmitter sa isang standby na estado.

Ang isang microcontroller na walang built-in na hardware circuit, halimbawa sa bit level, ay maaaring makapagpabagal sa bilis ng orasan sa pamamagitan ng pagtaas ng tagal ng kanilang mababang estado. Bilang resulta, ang baud rate ng master device ay matutukoy ng bilis ng mas mabagal na aparato.

PAG-ADRESS

Ang bawat device na nakakonekta sa I2C bus ay may natatanging program address kung saan tinutugunan ito ng master sa pamamagitan ng pagpapadala ng isang partikular na command. Ang mga microcircuits ng parehong uri ay nailalarawan sa pamamagitan ng isang tagapili ng address, na ipinatupad alinman sa anyo ng mga digital na input ng tagapili, o sa analog na anyo. Ang mga address ay nahahati sa address space ng mga device na nakakonekta sa bus.

Ipinapalagay ng normal na mode ang pitong-bit na pag-address. Ang pagtugon ay gumagana tulad ng sumusunod: pagkatapos ng utos na «START», ipinapadala ng master ang unang byte, na tumutukoy kung aling device ng alipin ang kailangan upang makipag-usap sa master. Mayroon ding karaniwang address ng tawag na tumutukoy sa lahat ng device sa bus, lahat ng device (theoretically) ay tumutugon dito nang may pagkilala, ngunit sa pagsasanay ay bihira ito.

Kaya ang unang pitong bits ng unang byte ay ang address ng alipin. Ang hindi bababa sa makabuluhang bit, ang ikawalo, ay nagpapahiwatig ng direksyon ng pagpapadala ng data. Kung mayroong «0», kung gayon ang impormasyon ay isusulat mula sa panginoon hanggang sa aliping ito. Kung «1», ang impormasyon ay babasahin ng amo mula sa aliping ito.

Matapos maipadala ng master ang address byte, inihahambing ng bawat alipin ang address nito dito. Ang sinumang may parehong address ay isang alipin at tinukoy bilang isang tagapaghatid ng alipin o tagatanggap ng alipin, depende sa halaga ng hindi bababa sa makabuluhang bit ng address byte.

Ang isang slave address ay maaaring magsama ng mga fixed at programmable na bahagi. Kadalasan ang isang malaking bilang ng mga aparato ng parehong uri ay gumagana sa isang system, pagkatapos ay pinapayagan ng programmable na bahagi ng address ang paggamit ng maximum ng parehong uri ng mga aparato sa bus. Gaano karaming mga bit sa address byte ang naa-program ay depende sa bilang ng mga libreng pin sa chip.

Minsan sapat na ang isang pin na may analog na setting ng programmable address range, halimbawa ang SAA1064 - isang driver ng LED indicator na may eksaktong ganoong pagpapatupad. Tinutukoy ng potensyal ng isang partikular na pin ang offset ng address space ng chip upang ang mga chip ng parehong uri ay hindi magkasalungat na tumatakbo sa parehong bus. Ang lahat ng mga chip na sumusuporta sa I2C bus ay naglalaman ng isang hanay ng mga address na tinukoy ng tagagawa sa dokumentasyon.

Ang kumbinasyon na «11110XX» ay nakalaan para sa 10-bit na pag-address. Kung isipin natin ang pagpapalitan ng data mula sa command na «START» patungo sa command na «STOP», magiging ganito ang hitsura:

Ang simple at pinagsamang mga format ng palitan ng data ay pinapayagan dito. Ang pinagsamang format ay nangangahulugan na sa pagitan ng «START» at «STOP» ang master at alipin ay maaaring kumilos bilang mga receiver at transmitters, ito ay kapaki-pakinabang halimbawa sa serial memory management.

Hayaang maglipat ng memory address ang unang byte ng data. Pagkatapos, ulitin ang utos na «START» at binabasa ang address ng alipin, gagana ang data ng memorya. Ang mga desisyon na awtomatikong dagdagan o bawasan ang dating na-access na address ay ginawa ng developer ng device pagkatapos na dati nang pag-aralan ang dokumentasyon ng chip. Sa isang paraan o iba pa, pagkatapos matanggap ang START command, ang lahat ng mga device ay dapat na ibalik ang kanilang lohika at maghanda para sa katotohanan na ang address ay papangalanan na ngayon.